- #MUX 4X1 VERILOG PROGRAMME BY USING 2X1 TEST BENCH HOW TO#

- #MUX 4X1 VERILOG PROGRAMME BY USING 2X1 TEST BENCH CODE#

#MUX 4X1 VERILOG PROGRAMME BY USING 2X1 TEST BENCH CODE#

You then send the select code to the decoder, and each output from the. How ro translate in to verilog code for both Mealy & Moore FSM with examples. Answer: You connect all four thee-state buffer outputs together (this becomes the MUX output). This courses shows clear picture on Finite State Machines (FSM) In practice they are not often used because they are limited to two one-bit inputs. A half-adder shows how two bits can be added together with a few simple logic gates. These examples includes, file based system tasks such as writing data in to file, reading data from file and loading data in to memory and random data generator. Half adders are a basic building block for new digital designers.

#MUX 4X1 VERILOG PROGRAMME BY USING 2X1 TEST BENCH HOW TO#

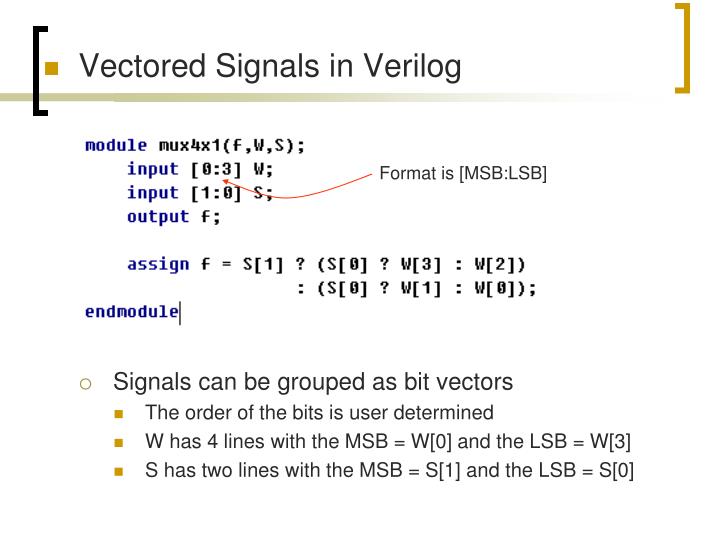

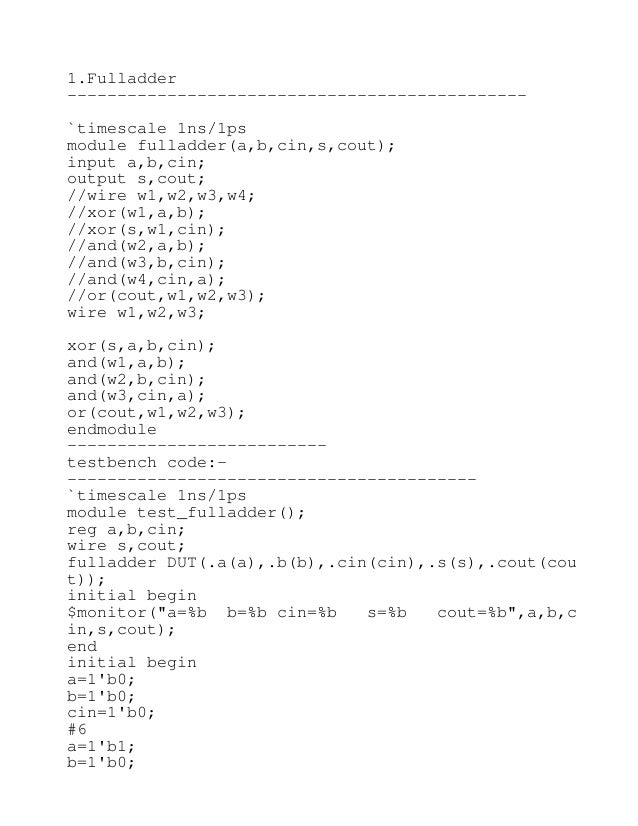

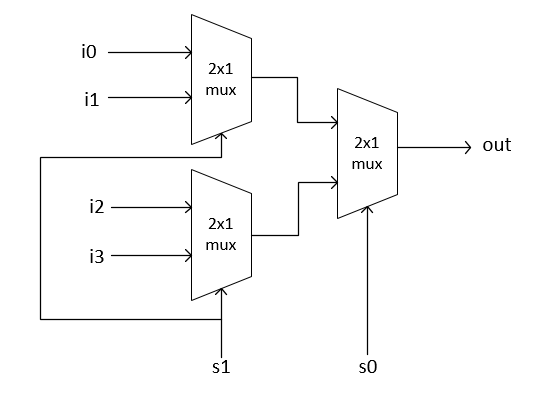

This courses explains how to write verification models using test benches with task and system tasks with Examples. simulation and writing a test bench and some general examples like counter, clock diver using counter, pulse generator. This course gives clear picture on verification, i.e. Write a VHD test bench to test your 4x1 multiplexer. This course gives information on different styles of programming like Gate level, Data flow, Behavioral and switch level with examples. Use the 2x1 multiplexer implemented in part (1) for the structural modeling.

In this course we give information related to VLSI design flow for FPGA & ASIC and gives overview about both. This course discuss the concepts in Verilog HDL programming and properties compared with C-Language and discussing the features and advantages. First signal should be output and then inputs. While using these primitives you should follow the connection rules. In this Verilog project, Verilog code for multiplexers such as 2-to-1 multiplexer, 2x5-to-5 multiplexer and 2x32-to-32 multiplexer are presented. Complete Verilog HDL programming course with a perfect, well structured and concise course for freshers and experienced, as it is from fundamental level to the application level. xor x1(y,a, b) //xor is a built in primitive. electronics Projects ieee MUX41 is ( Sel : in stdlogicvector(1 downto 0) MUX41 behavior of MUX41 is (Sel, A, B, C, D) (. Multiplexers are used for selecting one of many different digital inputs and forwarding to the output based on the controlling signals.

0 kommentar(er)

0 kommentar(er)